# MiniRISC<sup>®</sup> EZ4021-FC Building Blocks

# **Technical Manual**

April 2000

Order Number C14070

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

Document DB14-000108-00, First Edition April 2000 This document describes Revision A of the LSI Logic Corporation MiniRISC<sup>®</sup> EZ4021-FC EasyMACRO Building Blocks and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

#### To receive product literature, visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 1999, 2000 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design, CoreWare and CoreWare logo design, G12 and G12 logo design, FlexCore, FlexStream, GigaBlaze, Merlin, MiniRISC, MiniSIM, Right-First-Time, and SeriaLink are trademarks or registered trademarks of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

# Preface

This book is the primary reference and User's Guide for the MiniRISC<sup>®</sup> EZ4021-FC Microprocessor EasyMACRO Building Blocks. It contains a complete functional description for each building block.

#### Audience

This document assumes that you have some familiarity with microprocessors and related support devices. The people who benefit from this book are:

- Engineers and managers who are evaluating the EZ4021-FC building blocks for possible use in a system

- Engineers who are designing the processor and associated building blocks into a system

#### Organization

This document contains the following chapters and appendixes:

- Chapter 1, Introduction, introduces the EZ4021-FC feature set and briefly discusses the available building blocks.

- Chapter 2, **SDRAM Controller**, describes the EZ4021-FC SDRAM Controller and its operation.

- Chapter 3, Quick Bus, describes the EZ4021-FC's 64 bit high-performance on-chip bus, the QuickBus.

- Chapter 4, External Bus Controller, describes the External Bus Controller, which allows off-chip peripherals to communicate with the EZ4021-FC through the QuickBus.

#### **Related Publications**

*MiniRISC<sup>®</sup> EZ4021-FC Microprocessor EasyMACRO Technical Manual*, Document No. DB15-000080-01

#### **Conventions Used in This Manual**

The first time a word or phrase is defined in this manual, it is *italicized*.

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x" —for example, 0x32CF. Binary numbers are indicated by the prefix "0b" —for example, 0b0011.0010.1100.1111.

# Contents

| Chapter 1 | Intro | oduction |                                         |      |

|-----------|-------|----------|-----------------------------------------|------|

| -         | 1.1   | Systen   | n Overview                              | 1-1  |

|           | 1.2   | EZ402    | 1-FC Features                           | 1-3  |

|           | 1.3   | Buildin  | g Blocks Overview                       | 1-4  |

|           |       | 1.3.1    | SDRAM Controller                        | 1-4  |

|           |       | 1.3.2    | Quick Bus                               | 1-5  |

|           |       | 1.3.3    | External Bus Controller                 | 1-5  |

|           | 1.4   | MiniRI   | SC Support Tools                        | 1-5  |

|           | 1.5   | CoreW    | are Program                             | 1-6  |

|           |       | 1.5.1    | CoreWare Building Blocks                | 1-6  |

|           |       | 1.5.2    | Design Environment                      | 1-6  |

|           |       | 1.5.3    | Expert Support                          | 1-7  |

| Chapter 2 | SDR   | AM Con   | troller                                 |      |

|           | 2.1   | Overvi   | ew                                      | 2-1  |

|           | 2.2   | Feature  | es                                      | 2-2  |

|           | 2.3   | SDRA     | M Overview                              | 2-2  |

|           | 2.4   | SDRA     | M Types and Memory Area                 | 2-4  |

|           | 2.5   | SDRA     | M Controller and SDRAM Device Interface | 2-4  |

|           | 2.6   | SDRA     | M Addressing                            | 2-6  |

|           |       | 2.6.1    | Quick Bus to SDRAM Controller           | 2-6  |

|           |       | 2.6.2    | SDRAM Controller to SDRAM               | 2-7  |

|           | 2.7   | SDRA     | M Controller Signals                    | 2-8  |

|           |       | 2.7.1    | Signal Descriptions                     | 2-11 |

|           | 2.8   | Progra   | mming the SDRAM Mode Register           | 2-15 |

|           | 2.9   | SDRA     | M Commands                              | 2-16 |

|           |       | 2.9.1    | Row Active (ACTV) Command               | 2-17 |

|           |       | 2.9.2    | Mode Register Set (MRS) Command         | 2-18 |

|           |       | 2.9.3    | No Operation (NOP) Command              | 2-18 |

| 2.9.5 Precharge Selected Bank (PRE) (<br>2.9.6 Read (READ) Command<br>2.9.7 Refresh (REF) Command<br>2.9.8 Write (WRIT) Command<br>2.10 SDRAM Controller Registers<br>2.10.1 SDRAM Controller Configuration I<br>2.10.2 SDRAM Controller Refresh Regis<br>2.11 SDRAM Initializatio<br>2.12 Mbus Timing Waveforms<br>2.12.1 Single Transactions<br>2.12.2 Burst Transactions<br>2.12.2 Burst Transactions<br>2.12.3 Initialization<br>Chapter 3 Quick Bus<br>3.1 Overview and Features<br>3.2 Quick Bus Transactions<br>3.3 Device Attachment Criteria<br>3.4 Supported Devices<br>3.5 Signal Descriptions<br>3.5.1 Master - Command Signals<br>3.5.2 Master - Read Return Signals<br>3.5.3 Slave - Command<br>3.5.4 Slave - Read Return<br>3.6 Functional Description<br>3.6.1 Command Cycle<br>3.6.2 Read Return Cycle<br>3.6.3 Slave Ready Logic<br>3.6.4 Burst Transactions<br>3.6.5 Bus Locking<br>3.6.6 Bus Snooping<br>Chapter 4 External Bus Controller<br>4.1 Overview                                                        | nand 2-18     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 2.9.7 Refresh (REF) Command<br>2.9.8 Write (WRIT) Command<br>2.10 SDRAM Controller Registers<br>2.10.1 SDRAM Controller Configuration I<br>2.10.2 SDRAM Controller Refresh Regis<br>2.11 SDRAM Initializatio<br>2.12 Mbus Timing Waveforms<br>2.12.1 Single Transactions<br>2.12.2 Burst Transactions<br>2.12.3 Initialization<br>Chapter 3 Quick Bus<br>3.1 Overview and Features<br>3.2 Quick Bus Transactions<br>3.3 Device Attachment Criteria<br>3.4 Supported Devices<br>3.5 Signal Descriptions<br>3.5.1 Master - Command Signals<br>3.5.2 Master - Read Return Signals<br>3.5.3 Slave - Command<br>3.5.4 Slave - Read Return<br>3.6 Functional Description<br>3.6.1 Command Cycle<br>3.6.2 Read Return Cycle<br>3.6.3 Slave Ready Logic<br>3.6.4 Burst Transactions<br>3.6.5 Bus Locking<br>3.6.6 Bus Snooping                                                                                                                                                                                                                | Command 2-18  |

| 2.9.8 Write (WRIT) Command<br>2.10 SDRAM Controller Registers<br>2.10.1 SDRAM Controller Configuration I<br>2.10.2 SDRAM Controller Refresh Regis<br>2.11 SDRAM Initializatio<br>2.12 Mbus Timing Waveforms<br>2.12.1 Single Transactions<br>2.12.2 Burst Transactions<br>2.12.3 Initialization<br>Chapter 3 Quick Bus<br>3.1 Overview and Features<br>3.2 Quick Bus Transactions<br>3.3 Device Attachment Criteria<br>3.4 Supported Devices<br>3.5 Signal Descriptions<br>3.5.1 Master - Command Signals<br>3.5.2 Master - Read Return Signals<br>3.5.3 Slave - Command<br>3.5.4 Slave - Read Return<br>3.6 Functional Description<br>3.6.1 Command Cycle<br>3.6.2 Read Return Cycle<br>3.6.3 Slave Ready Logic<br>3.6.4 Burst Transactions<br>3.6.5 Bus Locking<br>3.6.6 Bus Snooping<br>Chapter 4 External Bus Controller                                                                                                                                                                                                          | 2-19          |

| 2.10       SDRAM Controller Registers         2.10.1       SDRAM Controller Configuration I         2.10.2       SDRAM Controller Refresh Regis         2.11       SDRAM Initializatio         2.12       Mbus Timing Waveforms         2.12.1       Single Transactions         2.12.2       Burst Transactions         2.12.3       Initialization    Chapter 3          Quick Bus         3.1       Overview and Features         3.2       Quick Bus Transactions         3.3       Device Attachment Criteria         3.4       Supported Devices         3.5       Signal Descriptions         3.5.1       Master - Command Signals         3.5.2       Master - Read Return Signals         3.5.3       Slave - Command         3.5.4       Slave - Read Return         3.6       Functional Description         3.6.1       Command Cycle         3.6.2       Read Return Cycle         3.6.3       Slave Ready Logic         3.6.4       Burst Transactions         3.6.5       Bus Locking         3.6.6       Bus Snooping | 2-19          |

| 2.10       SDRAM Controller Registers         2.10.1       SDRAM Controller Configuration I         2.10.2       SDRAM Controller Refresh Regis         2.11       SDRAM Initializatio         2.12       Mbus Timing Waveforms         2.12.1       Single Transactions         2.12.2       Burst Transactions         2.12.3       Initialization    Chapter 3          Quick Bus         3.1       Overview and Features         3.2       Quick Bus Transactions         3.3       Device Attachment Criteria         3.4       Supported Devices         3.5       Signal Descriptions         3.5.1       Master - Command Signals         3.5.2       Master - Read Return Signals         3.5.3       Slave - Command         3.5.4       Slave - Read Return         3.6       Functional Description         3.6.1       Command Cycle         3.6.2       Read Return Cycle         3.6.3       Slave Ready Logic         3.6.4       Burst Transactions         3.6.5       Bus Locking         3.6.6       Bus Snooping | 2-20          |

| 2.10.2 SDRAM Controller Refresh Regis<br>2.11 SDRAM Initializatio<br>2.12 Mbus Timing Waveforms<br>2.12.1 Single Transactions<br>2.12.2 Burst Transactions<br>2.12.3 Initialization<br>Chapter 3 Quick Bus<br>3.1 Overview and Features<br>3.2 Quick Bus Transactions<br>3.3 Device Attachment Criteria<br>3.4 Supported Devices<br>3.5 Signal Descriptions<br>3.5.1 Master - Command Signals<br>3.5.2 Master - Read Return Signals<br>3.5.3 Slave - Command<br>3.5.4 Slave - Read Return<br>3.6 Functional Description<br>3.6.1 Command Cycle<br>3.6.2 Read Return Cycle<br>3.6.3 Slave Ready Logic<br>3.6.4 Burst Transactions<br>3.6.5 Bus Locking<br>3.6.6 Bus Snooping<br>Chapter 4 External Bus Controller                                                                                                                                                                                                                                                                                                                      | 2-20          |

| 2.10.2 SDRAM Controller Refresh Regis<br>2.11 SDRAM Initializatio<br>2.12 Mbus Timing Waveforms<br>2.12.1 Single Transactions<br>2.12.2 Burst Transactions<br>2.12.3 Initialization<br>Chapter 3 Quick Bus<br>3.1 Overview and Features<br>3.2 Quick Bus Transactions<br>3.3 Device Attachment Criteria<br>3.4 Supported Devices<br>3.5 Signal Descriptions<br>3.5.1 Master - Command Signals<br>3.5.2 Master - Read Return Signals<br>3.5.3 Slave - Command<br>3.5.4 Slave - Read Return<br>3.6 Functional Description<br>3.6.1 Command Cycle<br>3.6.2 Read Return Cycle<br>3.6.3 Slave Ready Logic<br>3.6.4 Burst Transactions<br>3.6.5 Bus Locking<br>3.6.6 Bus Snooping<br>Chapter 4 External Bus Controller                                                                                                                                                                                                                                                                                                                      | Register 2-20 |

| 2.12       Mbus Timing Waveforms         2.12.1       Single Transactions         2.12.2       Burst Transactions         2.12.3       Initialization         Chapter 3         Quick Bus         3.1       Overview and Features         3.2       Quick Bus Transactions         3.3       Device Attachment Criteria         3.4       Supported Devices         3.5       Signal Descriptions         3.5.1       Master - Command Signals         3.5.2       Master - Read Return Signals         3.5.3       Slave - Command         3.5.4       Slave - Command         3.5.4       Slave - Read Return         3.6       Functional Description         3.6.1       Command Cycle         3.6.2       Read Return Cycle         3.6.3       Slave Ready Logic         3.6.4       Burst Transactions         3.6.5       Bus Locking         3.6.6       Bus Snooping                                                                                                                                                        |               |

| 2.12.1 Single Transactions<br>2.12.2 Burst Transactions<br>2.12.3 Initialization<br>Chapter 3 Quick Bus<br>3.1 Overview and Features<br>3.2 Quick Bus Transactions<br>3.3 Device Attachment Criteria<br>3.4 Supported Devices<br>3.5 Signal Descriptions<br>3.5.1 Master - Command Signals<br>3.5.2 Master - Read Return Signals<br>3.5.3 Slave - Command<br>3.5.4 Slave - Read Return<br>3.6 Functional Description<br>3.6.1 Command Cycle<br>3.6.2 Read Return Cycle<br>3.6.3 Slave Ready Logic<br>3.6.4 Burst Transactions<br>3.6.5 Bus Locking<br>3.6.6 Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-27          |

| 2.12.2 Burst Transactions<br>2.12.3 Initialization<br>Chapter 3 Quick Bus<br>3.1 Overview and Features<br>3.2 Quick Bus Transactions<br>3.3 Device Attachment Criteria<br>3.4 Supported Devices<br>3.5 Signal Descriptions<br>3.5.1 Master - Command Signals<br>3.5.2 Master - Read Return Signals<br>3.5.3 Slave - Command<br>3.5.4 Slave - Read Return<br>3.6 Functional Description<br>3.6.1 Command Cycle<br>3.6.2 Read Return Cycle<br>3.6.3 Slave Ready Logic<br>3.6.4 Burst Transactions<br>3.6.5 Bus Locking<br>3.6.6 Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-27          |

| 2.12.3 Initialization<br>Chapter 3 Quick Bus<br>3.1 Overview and Features<br>3.2 Quick Bus Transactions<br>3.3 Device Attachment Criteria<br>3.4 Supported Devices<br>3.5 Signal Descriptions<br>3.5.1 Master - Command Signals<br>3.5.2 Master - Read Return Signals<br>3.5.3 Slave - Command<br>3.5.4 Slave - Read Return<br>3.6 Functional Description<br>3.6.1 Command Cycle<br>3.6.2 Read Return Cycle<br>3.6.3 Slave Ready Logic<br>3.6.4 Burst Transactions<br>3.6.5 Bus Locking<br>3.6.6 Bus Snooping<br>Chapter 4 External Bus Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-28          |

| Chapter 3Quick Bus3.1Overview and Features3.2Quick Bus Transactions3.3Device Attachment Criteria3.4Supported Devices3.5Signal Descriptions3.5.1Master - Command Signals3.5.2Master - Read Return Signals3.5.3Slave - Command3.5.4Slave - Read Return3.6Functional Description3.6.1Command Cycle3.6.2Read Return Cycle3.6.3Slave Ready Logic3.6.4Burst Transactions3.6.5Bus Locking3.6.6Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-32          |

| 3.1Overview and Features3.2Quick Bus Transactions3.3Device Attachment Criteria3.4Supported Devices3.5Signal Descriptions3.5.1Master - Command Signals3.5.2Master - Read Return Signals3.5.3Slave - Command3.5.4Slave - Read Return3.6Functional Description3.6.1Command Cycle3.6.2Read Return Cycle3.6.3Slave Ready Logic3.6.4Burst Transactions3.6.5Bus Locking3.6.6Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-35          |

| 3.2       Quick Bus Transactions         3.3       Device Attachment Criteria         3.4       Supported Devices         3.5       Signal Descriptions         3.5.1       Master - Command Signals         3.5.2       Master - Read Return Signals         3.5.3       Slave - Command         3.5.4       Slave - Command         3.5.4       Slave - Read Return         3.6       Functional Description         3.6.1       Command Cycle         3.6.2       Read Return Cycle         3.6.3       Slave Ready Logic         3.6.4       Burst Transactions         3.6.5       Bus Locking         3.6.6       Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                  |               |

| 3.3Device Attachment Criteria3.4Supported Devices3.5Signal Descriptions3.5.1Master - Command Signals3.5.2Master - Read Return Signals3.5.3Slave - Command3.5.4Slave - Command3.6Functional Description3.6.1Command Cycle3.6.2Read Return Cycle3.6.3Slave Ready Logic3.6.4Burst Transactions3.6.5Bus Locking3.6.6Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-1           |

| 3.4Supported Devices3.5Signal Descriptions3.5.1Master - Command Signals3.5.2Master - Read Return Signals3.5.3Slave - Command3.5.4Slave - Read Return3.6Functional Description3.6.1Command Cycle3.6.2Read Return Cycle3.6.3Slave Ready Logic3.6.4Burst Transactions3.6.5Bus Locking3.6.6Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-3           |

| 3.5       Signal Descriptions         3.5.1       Master - Command Signals         3.5.2       Master - Read Return Signals         3.5.3       Slave - Command         3.5.4       Slave - Read Return         3.6       Functional Description         3.6.1       Command Cycle         3.6.2       Read Return Cycle         3.6.3       Slave Ready Logic         3.6.4       Burst Transactions         3.6.5       Bus Locking         3.6.6       Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-3           |

| 3.5.1       Master - Command Signals         3.5.2       Master - Read Return Signals         3.5.3       Slave - Command         3.5.4       Slave - Read Return         3.6       Functional Description         3.6.1       Command Cycle         3.6.2       Read Return Cycle         3.6.3       Slave Ready Logic         3.6.4       Burst Transactions         3.6.5       Bus Locking         3.6.6       Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-3           |

| 3.5.2       Master - Read Return Signals         3.5.3       Slave - Command         3.5.4       Slave - Read Return         3.6       Functional Description         3.6.1       Command Cycle         3.6.2       Read Return Cycle         3.6.3       Slave Ready Logic         3.6.4       Burst Transactions         3.6.5       Bus Locking         3.6.6       Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-4           |

| 3.5.3       Slave - Command         3.5.4       Slave - Read Return         3.6       Functional Description         3.6.1       Command Cycle         3.6.2       Read Return Cycle         3.6.3       Slave Ready Logic         3.6.4       Burst Transactions         3.6.5       Bus Locking         3.6.6       Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-7           |

| 3.5.4       Slave - Read Return         3.6       Functional Description         3.6.1       Command Cycle         3.6.2       Read Return Cycle         3.6.3       Slave Ready Logic         3.6.4       Burst Transactions         3.6.5       Bus Locking         3.6.6       Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-10          |

| 3.6       Functional Description         3.6.1       Command Cycle         3.6.2       Read Return Cycle         3.6.3       Slave Ready Logic         3.6.4       Burst Transactions         3.6.5       Bus Locking         3.6.6       Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-11          |

| 3.6.1       Command Cycle         3.6.2       Read Return Cycle         3.6.3       Slave Ready Logic         3.6.4       Burst Transactions         3.6.5       Bus Locking         3.6.6       Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-13          |

| 3.6.2       Read Return Cycle         3.6.3       Slave Ready Logic         3.6.4       Burst Transactions         3.6.5       Bus Locking         3.6.6       Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-14          |

| 3.6.3       Slave Ready Logic         3.6.4       Burst Transactions         3.6.5       Bus Locking         3.6.6       Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-14          |

| 3.6.4       Burst Transactions         3.6.5       Bus Locking         3.6.6       Bus Snooping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-18          |

| 3.6.5     Bus Locking       3.6.6     Bus Snooping   Chapter 4 External Bus Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-22          |

| 3.6.6 Bus Snooping Chapter 4 External Bus Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-23          |

| Chapter 4 External Bus Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-24          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-25          |

| 4.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-1           |

| 4.2 Local Bus Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-3           |

| 4.3 EBC Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-3           |

| 4.3.1 EBC Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-7           |

| 4.4 | EBC Tra  | ansactions                                  | 4-13 |

|-----|----------|---------------------------------------------|------|

|     | 4.4.1    | EZ4021-FC as Lbus Master                    | 4-14 |

|     | 4.4.2    | EZ4021-FC as Lbus Slave                     | 4-15 |

| 4.5 | EBC Re   | gisters                                     | 4-16 |

|     | 4.5.1    | EBC Watchdog Timer Failing Address Register | 4-16 |

|     | 4.5.2    | EBC Watchdog Timer Error Register           | 4-17 |

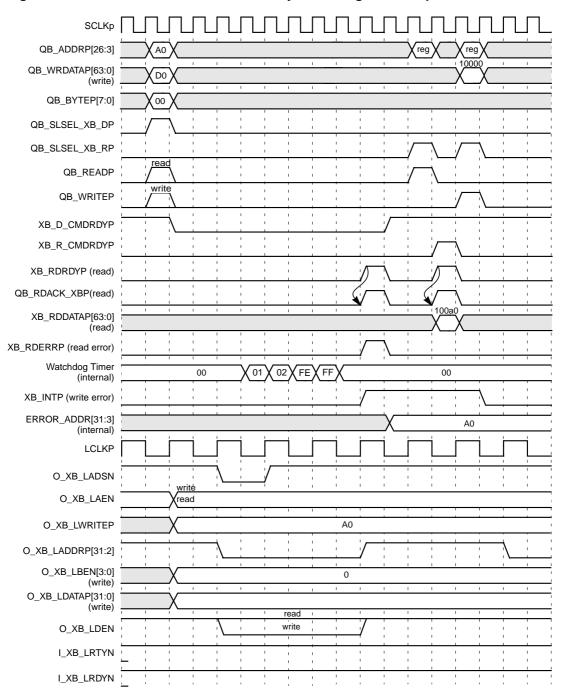

| 4.6 | Timing \ | Naveforms                                   | 4-17 |

|     | 4.6.1    | EZ4021-FC as Lbus Master                    | 4-18 |

|     | 4.6.2    | Lbus Device as Lbus Master                  | 4-25 |

|     | 4.6.3    | Lbus Transaction Termination by             |      |

|     |          | Watchdog Timer Expiration                   | 4-27 |

|     |          |                                             |      |

### **Customer Feedback**

# Figures

| 1.1  | EZ4021-FC in a Typical System                 | 1-2  |

|------|-----------------------------------------------|------|

| 2.1  | SDRAM Versus Standard DRAM Timing             | 2-3  |

| 2.2  | SDRAM Controller and SDRAM Array Interface    | 2-5  |

| 2.3  | SDRAM Controller Address Bit Assignment       |      |

|      | (QB_ADDRP[31:0])                              | 2-7  |

| 2.4  | 64 Mbit SDRAM Device Address Bit Assignment   |      |

|      | (O_SADDRP[13:0]                               | 2-8  |

| 2.5  | SDRAM Controller Connection Diagram           | 2-9  |

| 2.6  | SDRAM Mode Register                           | 2-15 |

| 2.7  | SDRAM Controller Configuration Register (R/W) | 2-21 |

| 2.8  | SDRAM Controller Refresh Register (R/W)       | 2-26 |

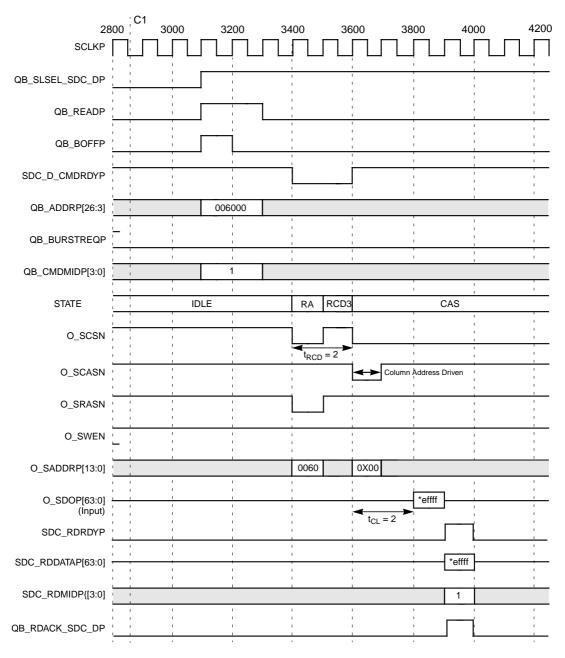

| 2.9  | Single Read Transaction ( $CL = 2$ )          | 2-29 |

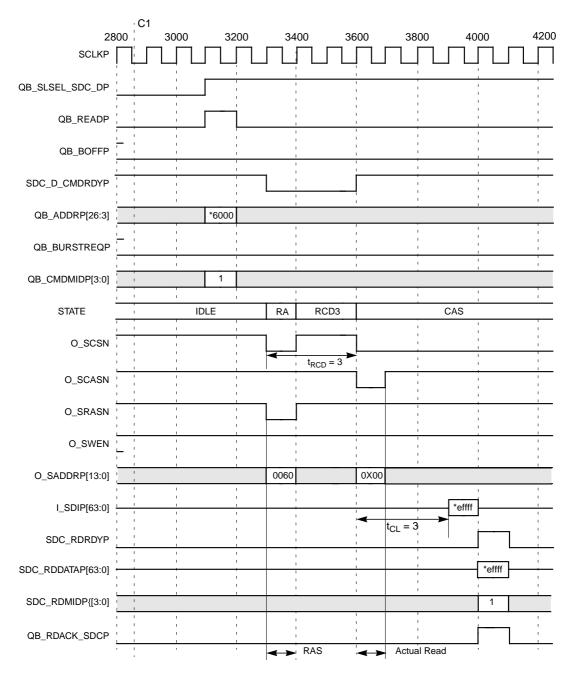

| 2.10 | Single Read Transaction (CL = 3)              | 2-30 |

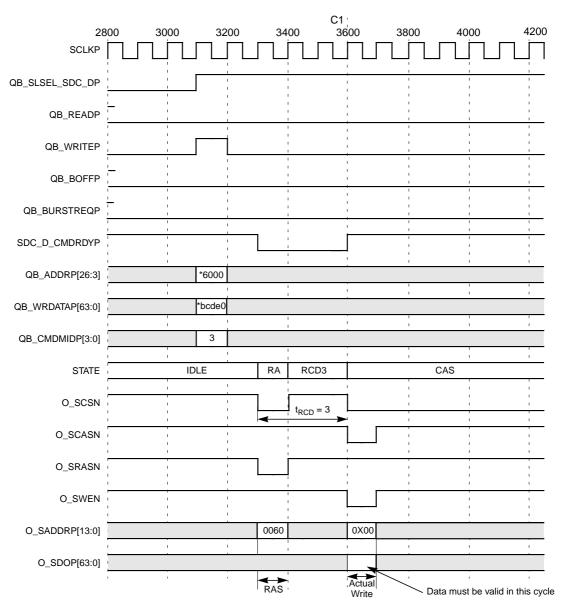

| 2.11 | Single Write Transaction                      | 2-31 |

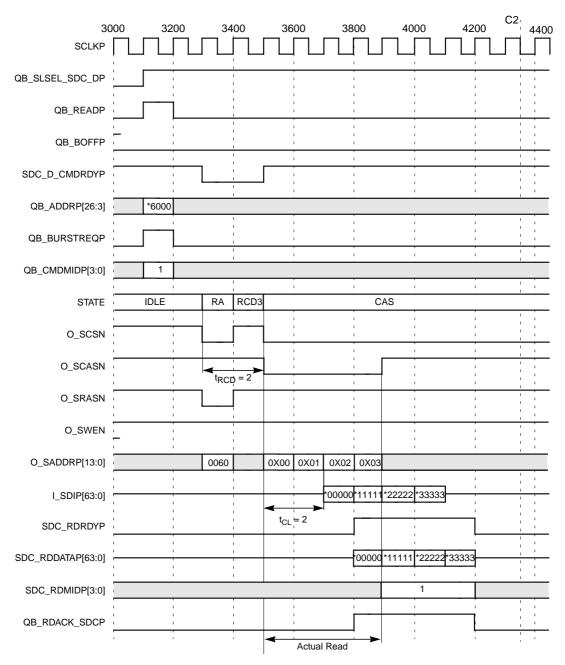

| 2.12 | Burst Read Transaction (CL = 2)               | 2-33 |

| 2.13 | Burst Write Transaction                       | 2-34 |

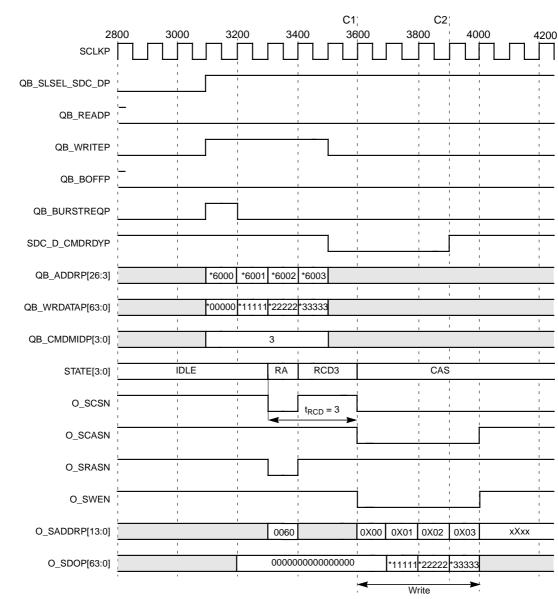

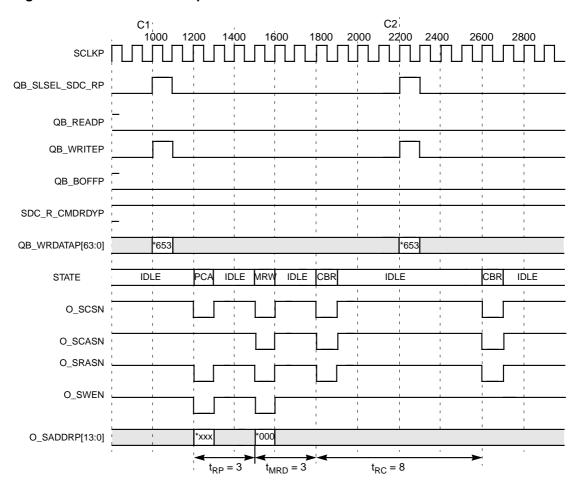

| 2.14 | Initialization Sequence                       | 2-35 |

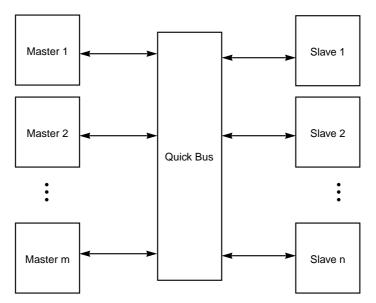

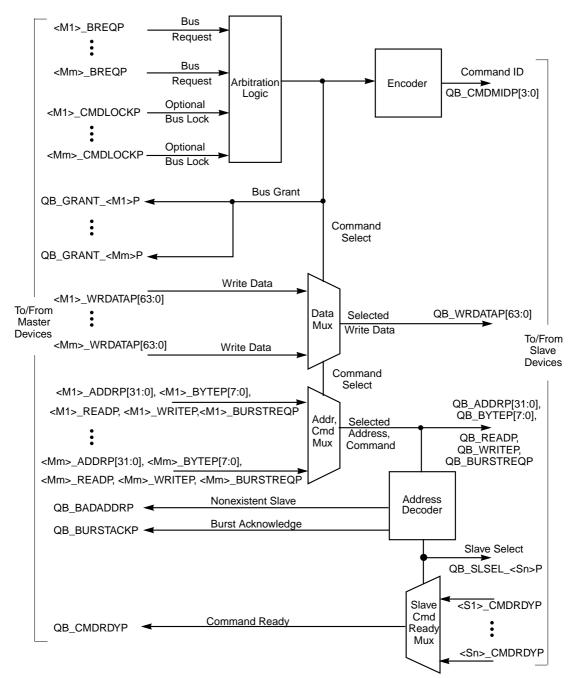

| 3.1  | Quick Bus Block Diagram                       | 3-2  |

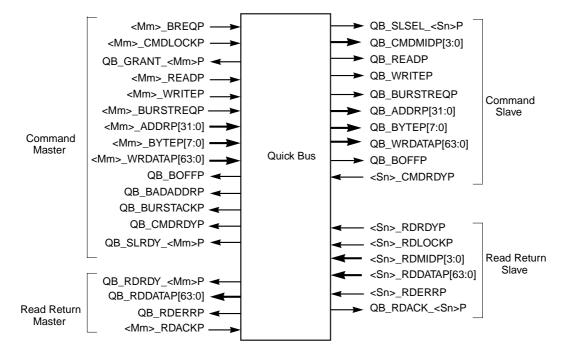

| 3.2  | Quick Bus Signals                             | 3-5  |

| 3.3  | Typical Quick Bus Command Logic               | 3-15 |

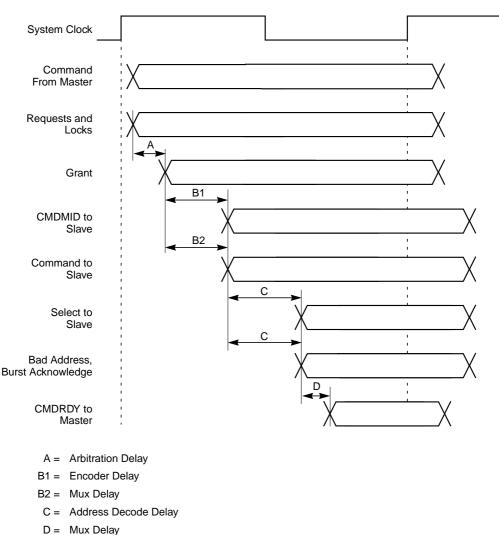

| 3.4  | Quick Bus Command Timing                      | 3-18 |

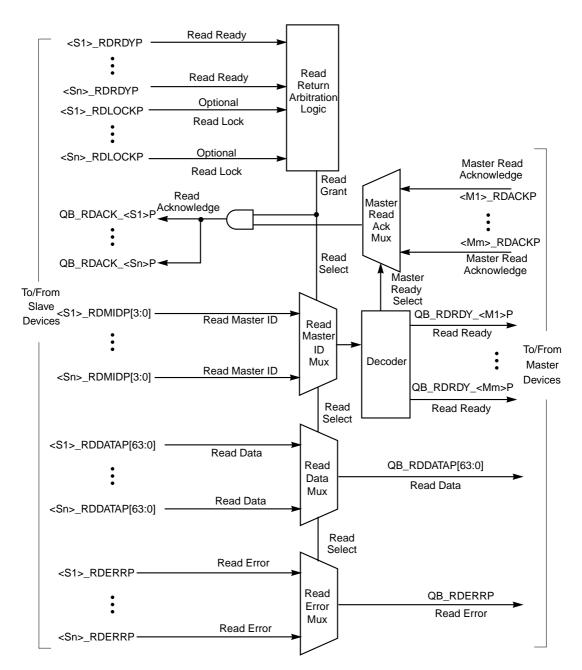

| 3.5  | Typical Quick Bus Read Return Logic           | 3-20 |

|      |                                               |      |

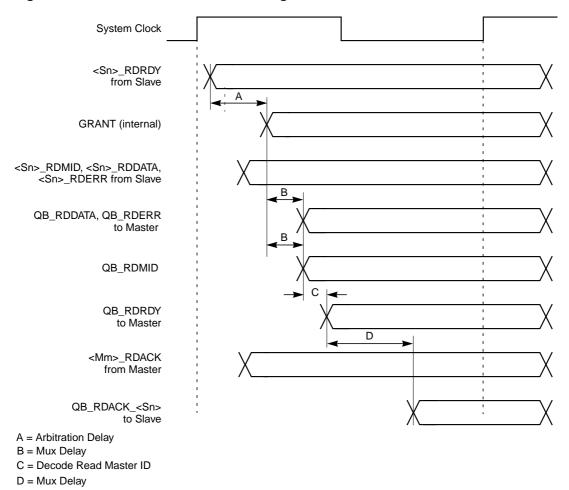

| 3.6  | Quick Bus Read Return Timing                                 | 3-22 |

|------|--------------------------------------------------------------|------|

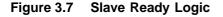

| 3.7  | Slave Ready Logic                                            | 3-23 |

| 3.8  | Four-Word Burst Lock Example                                 | 3-24 |

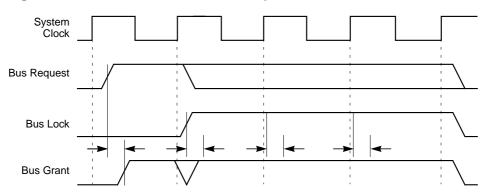

| 3.9  | Snoop Interface                                              | 3-26 |

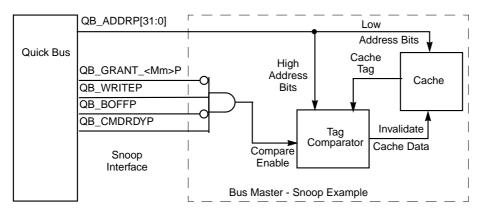

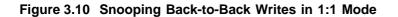

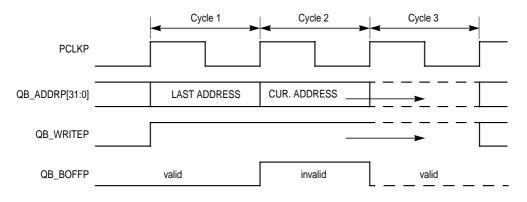

| 3.10 | Snooping Back-to-Back Writes in 1:1 Mode                     | 3-27 |

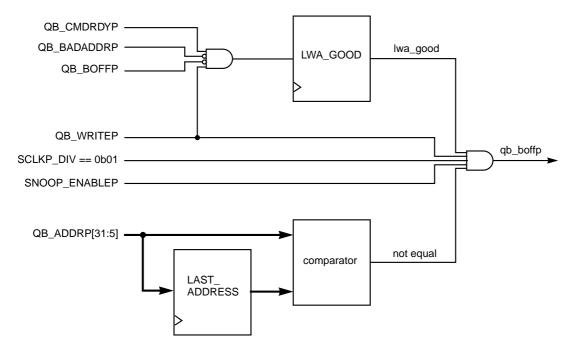

| 3.11 | Logic for Generating Backoff                                 | 3-28 |

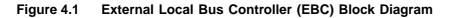

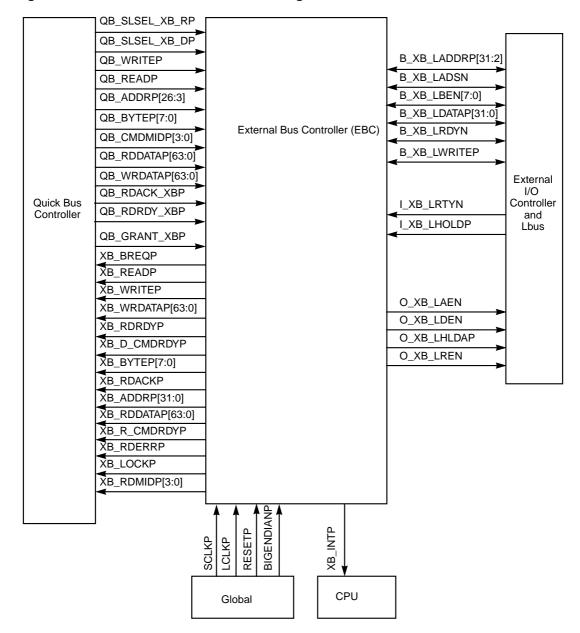

| 4.1  | External Local Bus Controller (EBC) Block Diagram            | 4-2  |

| 4.2  | EBC Controller Connection Diagram                            | 4-4  |

| 4.3  | EBC Watchdog Timer Failing Address Register                  | 4-16 |

| 4.4  | Watchdog Timer Error Register                                | 4-17 |

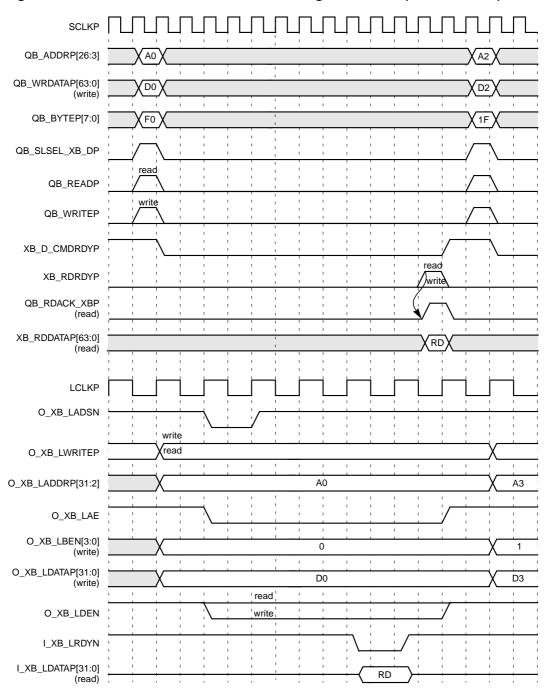

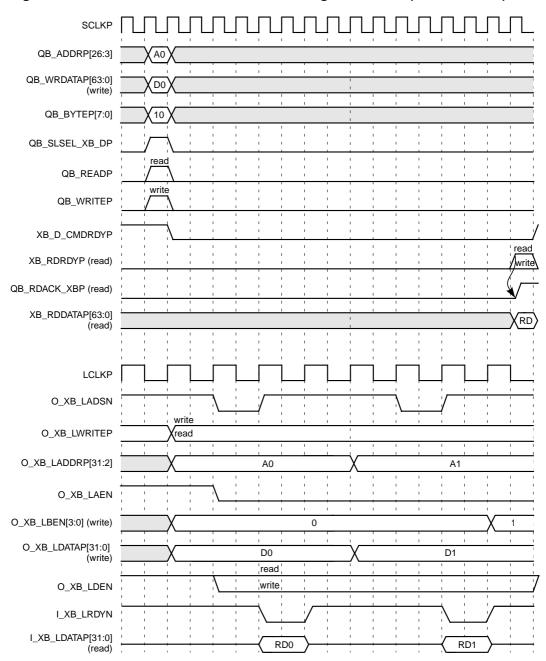

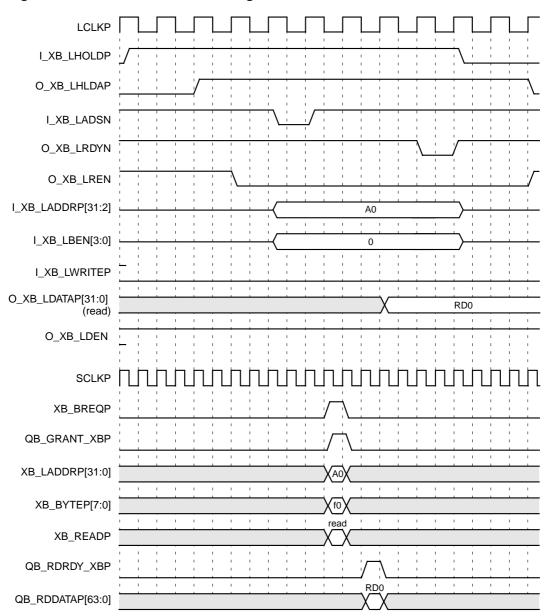

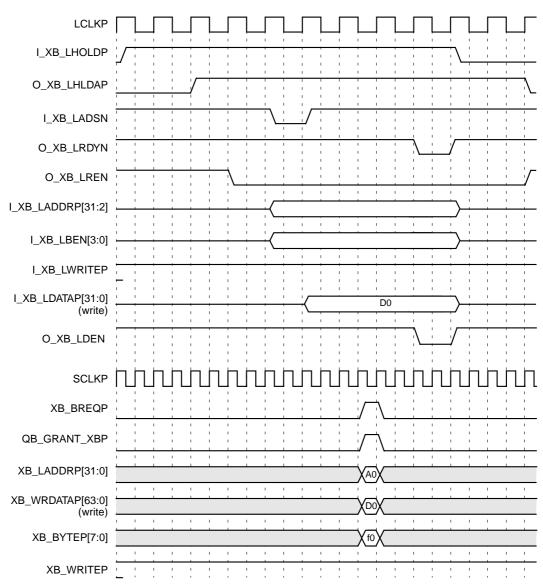

| 4.5  | Quick Bus Master Read/Write Timing Waveforms (32 Bit Access) | 4-20 |

| 4.6  | Quick Bus Master Read/Write Timing Waveforms                 | 4-20 |

| 4.0  | (64 Bit Access)                                              | 4-22 |

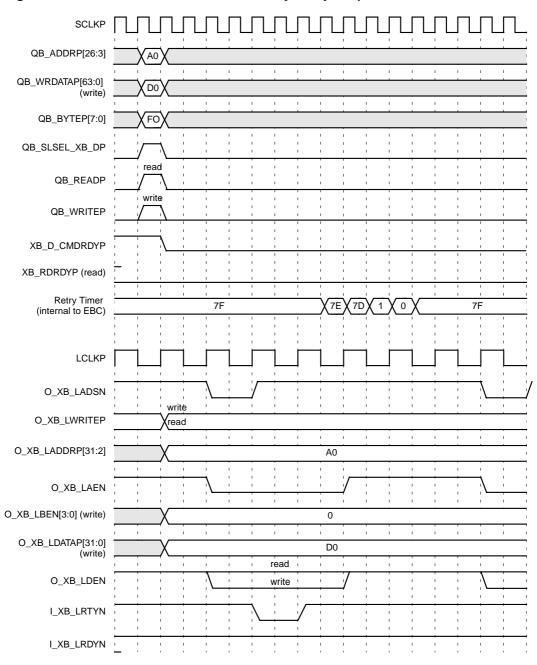

| 4.7  | Lbus Transaction Terminated by Retry Request                 | 4-24 |

| 4.8  | Lbus Master Read Timing Waveforms                            | 4-26 |

| 4.9  | Lbus Master Write Timing Waveforms                           | 4-27 |

| 4.10 | Lbus Transaction Terminated by Watchdog                      |      |

|      | Timer Expiration                                             | 4-29 |

|      |                                                              |      |

# Tables

| 2.1 | SDRAM Types and Available Memory Area            | 2-4  |

|-----|--------------------------------------------------|------|

| 2.2 | SDRAM Controller Address Bit Assignments         |      |

|     | (QB_ADDRP[31:0])                                 | 2-7  |

| 2.3 | SDRAM Controller Alphabetical Signal List        | 2-9  |

| 2.4 | SDRAM Command Summary (64 Mbit Mode)             | 2-17 |

| 2.5 | Configuration Register Programming Example       | 2-25 |

| 2.6 | SDRAM Refresh Register Programming Value         | 2-26 |

| 2.7 | STATE Acronyms                                   | 2-28 |

| 3.1 | Quick Bus Signal Summary                         | 3-5  |

| 4.1 | Lbus Features                                    | 4-3  |

| 4.2 | External Bus Controller Alphabetical Signal List | 4-5  |

# Chapter 1 Introduction

This chapter introduces the building blocks available with the LSI Logic MiniRISC EZ4021-FC Microprocessor Core.

The chapter contains the following sections:

- Section 1.1, "System Overview," page 1-1

- Section 1.2, "EZ4021-FC Features," page 1-3

- Section 1.3, "Building Blocks Overview," page 1-4

- Section 1.4, "MiniRISC Support Tools," page 1-5

- Section 1.5, "CoreWare Program," page 1-6

# 1.1 System Overview

The MiniRISC EZ4021-FC Microprocessor EasyMACRO core is a compact, high-performance, 64-bit microprocessor subsystem. The EZ4021-FC uses the LSI Logic CoreWare<sup>®</sup> system-on-a-chip methodology and executes the MIPS III instruction set. It is ideal for high-performance, cost-sensitive embedded processor applications.

For detailed information about the EZ4021-FC, see the *MiniRISC EZ4021FC Microprocessor Core Technical Manual*.

You can easily design the EZ4021-FC into a wide range of products. It can be combined with industry standard cores and proprietary functional building blocks to create a completely customized embedded system on a chip.

LSI Logic currently provides the following building blocks:

SDRAM Controller (SDRAMC), described in Chapter 2, "SDRAM Controller."

- Quick Bus, described in Chapter 3, "Quick Bus."

- External Bus Controller (EBC), described in Chapter 4, "External Bus Controller."

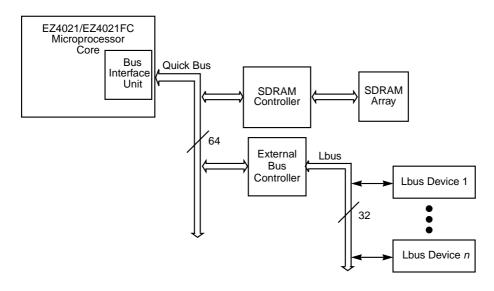

The building blocks are briefly described in Section 1.3, "Building Blocks Overview." System designers can use these building blocks as they are provided, or modify them for specific needs. Figure 1.1 shows how the EZ4021-FC Microprocessor Core interfaces with building blocks in a typical design.

#### Figure 1.1 EZ4021-FC in a Typical System

# 1.2 EZ4021-FC Features

This section summarizes the key features of the EZ4021-FC.

- High-performance RISC CPU core for CoreWare ASIC

- Single issue, five-stage pipeline

- 250 native MIPS, 250+ Dhrystone MIPS at 250 MHz

- 250-MHz operation at WC125 (Tj = 125 °C, VDD = 1.71 V, worst-case process)

- MIPS III Instruction Set Architecture (ISA)

- Thirty-two 64-bit general-purpose registers

- 32-bit wide MIPS III ISA supporting 64-bit integer operations

- R4000-style status register and exception processing

- Wait for Interrupt (WAITI) instruction for power saving

- Supports SPECIAL2 Multiply-Accumulate extensions

- Both big and little endian support for load and store operations

- Integrated multiplier and divider

- High-performance eight bit/cycle multiplier

- 32-bit unsigned or signed multiplication in five CPU clock cycles

- 64-bit unsigned or signed multiplication in nine CPU clock cycles

- Compact and low performance (1 bit/cycle) divider

- 32-bit unsigned or signed division in 34 CPU clock cycles

- 64-bit unsigned or signed division in 66 CPU clock cycles

- Integrated instruction and data caches (Harvard architecture)

- MMU implements 32 dual-entry page translations

- 16 Kbyte 2-way set-associative instruction cache

- ♦ Least Recently Used (LRU) algorithm for replacement

- Line level lock for instruction cache RAM

- 16 Kbyte 2-way set-associative data cache

- LRU algorithm for replacement

- ♦ Line level lock for scratchpad memory

- Write-through or write-back update policy, programmable on a per-page basis

- Integrated EJTAG debug support features

- MIPS products standard EJTAG 1.5.3 compliant

- Simple instruction and data breakpoints

- Or Program Counter (PC) trace

- O Processor single step and software debug breakpoints

- System Coprocessor Zero (CP0) Count and Compare registers

- MIPS CPU standard interrupt exceptions (one NMI, one timer, five hardware, two software)

- Serial scan for device testing and EJTAG support for on-chip system debug

- 13 mm<sup>2</sup> core size

- 1.8 V Core VDD

- LSI Logic G12<sup>™</sup> CMOS technology (0.18 μ L-drawn, 0.15 μ L-effective)

# 1.3 Building Blocks Overview

This section gives a brief overview of the available EZ4021-FC building blocks.

### 1.3.1 SDRAM Controller

The SDRAM Controller allows an EZ4021-FC-based design to interface directly to a 64 Mbit SDRAM array without the need for external logic. The SDRAM Controller generates all commands for the SDRAM array, including Row Address Select (RAS) and Column Address Select (CAS).

The SDRAM Controller supports up to 64 Mbytes of SDRAM.

### 1.3.2 Quick Bus

The Quick Bus is a demultiplexed 32-bit address, 64-bit data split-transaction on-chip bus. It permits the overlap of command request and data return operations. This feature allows for higher bus utilization and the ability to hide long memory latency times to off-chip devices. The Quick Bus also supports multiple bus masters and data burst transactions.

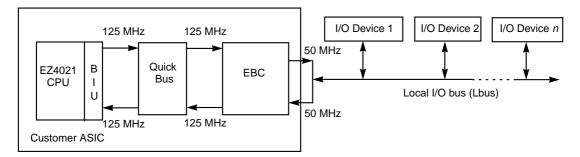

### 1.3.3 External Bus Controller

The External Bus Controller (EBC) allows the EZ4021-FC to interface to off-chip devices, such as ethernet controllers, serial I/O devices, and ROMs. The EBC serves as a bridge between the on-chip Quick Bus and the off-chip Local Bus (Lbus). The Lbus is a 32-bit multiplexed address/data bus.

External bus masters on the Lbus can arbitrate for ownership of the Local Bus and thereby make read and write requests on the Quick Bus.

The EBC supports a retry mechanism that can be used if a peripheral device cannot complete a request. The target device can assert retry, which causes the EBC to retry the transaction at a later time.

# 1.4 MiniRISC Support Tools

The EZ4021-FC has all the tools needed to develop a system on a chip, including:

- The LSI Logic MiniSIM<sup>®</sup>-20 architectural simulator

- Verilog models

- A system verification environment

- A PROM monitor

- Third-party software support

- A full-featured core evaluation chip (EV4020)

- Bus functional model for Quick Bus

# 1.5 CoreWare Program

The CoreWare program consists of three main elements:

- A library comprised of a wide range of complex cores based on accepted and emerging industry standards. The library includes high-speed interconnection, digital video, digital signal processing (DSP), and other cores.

- A design development and simulation package. LSI Logic provides a complete framework for device and system development and simulation. The LSI Logic advanced ASIC technologies consistently produce Right-First-Time<sup>™</sup> silicon.

- Support for expert applications. The LSI Logic in-house experts provide design support from system architecture definition through chip layout and test vector generation.

Using the CoreWare program, you can combine the EZ4021-FC microprocessor core with other cores on a single chip to create products uniquely suited to specific applications. The program provides unparalleled design flexibility and lets you create high-quality, leading edge products for a wide range of markets.

# 1.5.1 CoreWare Building Blocks

The CoreWare building blocks include elements based on the LSI Logic high-performance standard products, as well as other industry-standard products. The CoreWare building blocks, which include embedded MiniRISC MIPS processors, bus interface controllers, and a family of floating-point processors, are fully supported library elements for use in the LSI Logic hardware development environment. The building blocks include gate-level simulation models with timing information, so that designers can accurately simulate device performance and trade off various implementation options. In addition to gate-level simulation models, the building blocks also include behavioral simulation models.

# 1.5.2 Design Environment

ASIC families are supported by the LSI Logic comprehensive system-ona-chip design methodology. This design methodology uses both internally developed and industry-standard tools integrated with FlexStream<sup>®</sup> software and libraries that lets you use third-party software to access LSI Logic technology. You can select from a suite of industry standard simulators, synthesizers, timing analyzers, and test tools that are seamlessly integrated into a common environment for verification and sign-off.

# 1.5.3 Expert Support

The LSI Logic in-house experts support the CoreWare program with high-level design experience in a wide variety of application areas. These experts provide design support from system architecture definition through chip layout and test-vector generation. They help determine how many functions can be integrated on a single chip to find the most cost-effective solution.

# Chapter 2 SDRAM Controller

This chapter explains the operation of the EZ4021-FC's on-chip synchronous DRAM controller, and contains the following sections:

- Section 2.1, "Overview," page 2-1

- Section 2.2, "Features," page 2-2

- Section 2.3, "SDRAM Overview," page 2-2

- Section 2.4, "SDRAM Types and Memory Area," page 2-4

- Section 2.5, "SDRAM Controller and SDRAM Device Interface," page 2-4

- Section 2.6, "SDRAM Addressing," page 2-6

- Section 2.7, "SDRAM Controller Signals," page 2-8

- Section 2.8, "Programming the SDRAM Mode Register," page 2-15

- Section 2.9, "SDRAM Commands," page 2-16

- Section 2.10, "SDRAM Controller Registers," page 2-20

- Section 2.11, "SDRAM Initialization," page 2-27

- Section 2.12, "Mbus Timing Waveforms," page 2-27

# 2.1 Overview

The on-chip synchronous DRAM (SDRAM) controller interfaces directly to a 64 Mbit SDRAM memory array, eliminating the need for discrete control logic. This approach saves board space, reduces component count and design complexity, and increases performance by eliminating the inherent delays caused by external discrete components.

# 2.2 Features

The EZ4021-FC SDRAM Controller operates with industry-standard 64 Mbit devices (4-, 8-, and 16-bit wide) at clock frequencies up to 125 MHz, and offers the following features:

In-Page Hits

The SDRAM Controller supports in-page hits (also known as row parking). Once a row address is latched into a bank of the SDRAM, subsequent column addresses in the same row are clocked out according to the programmed column latency. No precharge is required. Each internal bank can store a row address.

• Quick Bus Optimized

The SDRAM Controller is optimized for use with the Quick Bus. Due to the split transaction nature of the Quick Bus, the requesting device may not immediately acknowledge the output data when it is latched by the SDRAM Controller. The controller output buffer stores output data until the Quick Bus is ready to read. As long as the write buffer is not full, the SDRAM Controller accepts read requests from the Quick Bus. If a burst read request is received while data is in the output buffer, the SDRAM Controller queues the read request and reissues it when the output buffer empties.

• Four Doubleword (Burst) Transaction

The SDRAM Controller does not support burst mode; all transactions are sequential. However, a four-doubleword request acts as a burst transaction. The SDRAM Controller performs four sequential accesses from a single address. The term *burst* in this document refers to the four-doubleword transaction.

# 2.3 SDRAM Overview

SDRAMs offer significant performance advantages over standard Fast Page Mode (FPM) or Extended Data Out (EDO) DRAM devices. In standard DRAM architectures, once the processor has requested data, it must wait for a certain number of clocks until data is returned. The amount of delay depends on the design of the memory system and the speed of the DRAMs used. In standard DRAM, the Row Address Select (RAS) and Column Address Select (CAS) signals must be held active from the start of the cycle until data is retrieved, which means that the DRAM cannot accept new cycle information during this time. Design techniques such as interleaving multiple memory banks helps address this latency problem. With this approach, subsequent accesses go to alternate banks, hiding some of the DRAM latency time. Interleaved memory systems achieve a performance boost over their noninterleaved counterparts, but require large amounts of real estate and increase the controller complexity.

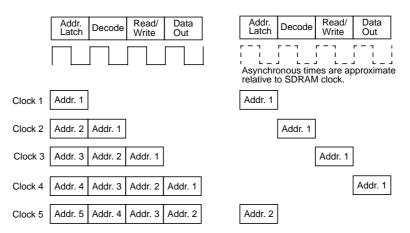

The clocked nature of the SDRAM allows for pipelining. New cycle information is driven to the array on every clock. Once the pipeline is filled, data can be driven out of the SDRAM on each subsequent clock. In addition, each 64 Mbit SDRAM device contains four internal banks, allowing for the implementation of an interleaved memory system without the added component count and controller complexity. Figure 2.1 shows a timing diagram comparing SDRAM and standard DRAM accesses. DRAM devices are asynchronous—access times in Figure 2.1 are relative to an SDRAM device with an equivalent access time.

#### Figure 2.1 SDRAM Versus Standard DRAM Timing

SDRAMs contain an on-chip mode register that provides a high degree of programmability. On-chip burst counters allow for the support of burst mode without the need for an external discrete counter to increment subsequent addresses of the burst. Column Address Select (CAS) latency, the number of clocks between the time data is requested and the time it is driven onto the bus, is also programmable. The higher the latency, the longer it takes to retrieve the first data item.

# 2.4 SDRAM Types and Memory Area

The SDRAM Controller supports 64 Mbit SDRAM devices with 4-, 8-, and 16-bit wide data buses. The 64M bit in the SDRAM Configuration Register must be set. Refer to Section 2.10.1, "SDRAM Controller Configuration Register," on page 2-20 for more information on the 64M bit.

Table 2.1 shows available SDRAM types, the total number of SDRAM devices required to design a memory system, the total memory size requirements, and the available address ranges.

Table 2.1SDRAM Types and Available Memory Area

| SDRAM Type         | Devices<br>Needed | Total Memory<br>Size | Address Area            |

|--------------------|-------------------|----------------------|-------------------------|

| 4 Mwords x 16 bits | 4                 | 32 Mbytes            | 0x0000.0000-0x01FF.FFFF |

| 8 Mwords x 8 bits  | 8                 | 64 Mbytes            | 0x0000.0000-0x03FF.FFFF |

| 16 Mwords x 4 bits | 16                | 128 Mbytes           | 0x0000.0000-0x07FF.FFFF |

# 2.5 SDRAM Controller and SDRAM Device Interface

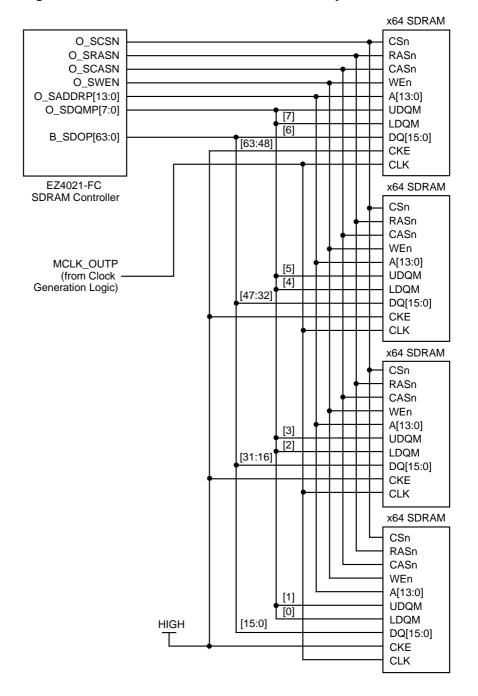

The SDRAM Controller interfaces to the SDRAM array without external glue logic. Figure 2.2 shows a connection diagram for a 1 Mword x 16-bit type SDRAM.

Figure 2.2 SDRAM Controller and SDRAM Array Interface

You must strap the the clock enable (CKE) input HIGH on all SDRAM devices, because the SDRAM Controller does not have a separate CKE signal. Strapping the input HIGH permanently enables the SDRAM devices.

The EZ4021-FC provides the clock for the SDRAM array. Although the EZ4021-FC internally adjusts the phase, the skew in the SDRAM array must be carefully monitored. Placing the devices as close together as possible alleviates some of the skew. Multiple clocks, each derived from the master memory clock, can be used if the array is large.

# 2.6 SDRAM Addressing

The EZ4021-FC SDRAM Controller passes address information between the Quick Bus and the SDRAM array. The SDRAM Controller receives a 32-bit address from the Quick Bus and communicates with the SDRAM array using the SDRAM 14-bit address bus.

64 Mbit SDRAM devices contain four internal banks. Row address bits O\_SADDRP[13:12] select the bank. One row address, specified by row address bits [11:0], is kept in each bank. All four banks may be activated independently.

The controller manages four pages (banks), which are selected by row address bits [13:12]. The SDRAM Controller also holds four sets of address bits [22:11].

# 2.6.1 Quick Bus to SDRAM Controller

The Quick Bus communicates with the SDRAM Controller using a 32-bit bus, QB\_ADDRP[31:0]. The valid bits are encoded in the QB\_ADDRP[26:3] signal. Figure 2.3 shows the address bit assignment for the SDRAM Controller.

#### Figure 2.3 SDRAM Controller Address Bit Assignment (QB\_ADDRP[31:0])

| 31       | 27 | 26 | 25 | 24 | 23 | 22  | 21  | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2 | 1 0           |   |

|----------|----|----|----|----|----|-----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---------------|---|

| Reserved |    | C9 | C8 | В1 | в0 | R11 | R10 | R9 | R8 | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 | C7 | C6 | C5 | C4 | СЗ | C2 | C1 | C0 |   | Byte<br>elect | ] |

Table 2.2 lists the bit assignments of the address bus shown in Figure 2.3.

#### Table 2.2 SDRAM Controller Address Bit Assignments (QB\_ADDRP[31:0])

| Address<br>Bits | Description                                                                                                                                                                                                                                                                                                  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:27           | These bits must be zero. The SDRAM Controller does not respond to the transaction if any of these bits are nonzero.                                                                                                                                                                                          |

| 26:25           | These bits are assigned to column address bits [9:8]. When 8-bit wide SDRAMs are used, bit 25 is ignored. When 16-bit wide devices are used, both bits are ignored.                                                                                                                                          |

| 24:23           | This signal selects one of four internal banks. Note that these banks reside internal to each SDRAM device. A value of 0b00 on these bits selects internal bank 0, 0b01 selects bank 1, 0b10 selects bank 2, and 0b11 selects bank 3. These bits are used as bits 13:12 for both the row and column address. |

| 22:11           | SDRAM row address [11:0].                                                                                                                                                                                                                                                                                    |

| 10:3            | SDRAM column address [7:0]                                                                                                                                                                                                                                                                                   |

| 2:0             | These three bits are ignored during all operation.                                                                                                                                                                                                                                                           |

# 2.6.2 SDRAM Controller to SDRAM

The SDRAM Controller communicates with the SDRAM devices using a 14-bit bus, O\_SADDRP[13:0]. Row addresses are driven separately from column addresses. Figure 2.4 shows the row and column address bit assignments for 4-, 8-, and 16-bit wide 64 Mbit SDRAM devices. In Figure 2.4, an x indicates a don't care.

# Figure 2.4 64 Mbit SDRAM Device Address Bit Assignment (O\_SADDRP[13:0]

Row Addressing for all 64 Mbit SDRAM Devices

| 13 | 12 | 11  | 10  | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| B1 | B0 | R11 | R10 | R9 | R8 | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

Column Addressing for 4-bit wide 64 Mbit SDRAM Devices

| 13 |    |   |   | -  | -  | -  | -  | -  | -  | -  | _  | -  | -  |

|----|----|---|---|----|----|----|----|----|----|----|----|----|----|

| B1 | B0 | х | 0 | C9 | C8 | C7 | C6 | C5 | C4 | C3 | C2 | C1 | C0 |

Column Addressing for 8-bit wide 64 Mbit SDRAM Devices

| 13 |    |   | - | - | -  |    | -  | -  |    | -  |    |    | -  |

|----|----|---|---|---|----|----|----|----|----|----|----|----|----|

| B1 | B0 | х | 0 | х | C8 | C7 | C6 | C5 | C4 | C3 | C2 | C1 | C0 |

Column Addressing for 16-bit wide 64 Mbit SDRAM Devices

| 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|---|---|----|----|----|----|----|----|----|----|

| B1 | B0 | х  | 0  | х | х | C7 | C6 | C5 | C4 | C3 | C2 | C1 | C0 |

# 2.7 SDRAM Controller Signals

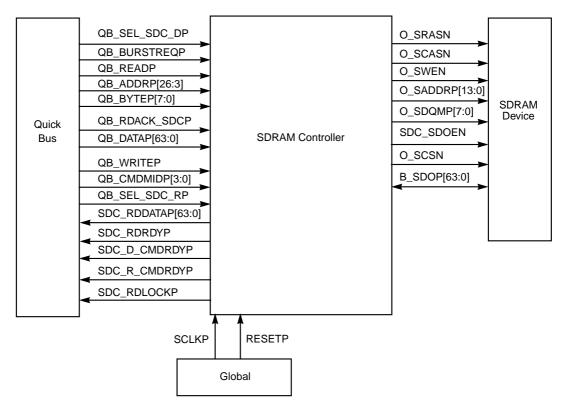

This section describes the SDRAM Controller signals, which are listed in Table 2.3. Figure 2.5 shows the connections between the Quick Bus controller, the SDRAM Controller, and the SDRAM array. Refer to Figure 2.2 on page 5 for more details on the SDRAM Controller to SDRAM array connections.

#### Figure 2.5 SDRAM Controller Connection Diagram

#### Table 2.3 SDRAM Controller Alphabetical Signal List

| Signal Name    | Input/Output  | Source                     | Destination                | Description                                 |

|----------------|---------------|----------------------------|----------------------------|---------------------------------------------|

| B_SDOP[63:0]   | Bidirectional | SDRAM Array<br>SDRAM Cont. | SDRAM Cont.<br>SDRAM Array | Read data from SDRAM<br>Write data to SDRAM |

| O_SADDRP[13:0] | Output        | SDRAM Cont.                | SDRAM Array                | Address                                     |

| O_SCASN        | Output        | SDRAM Cont.                | SDRAM Array                | Column Address Select<br>(CAS) Command      |

| O_SCSN         | Output        | SDRAM Cont.                | SDRAM Array                | Chip Select                                 |

| O_SDQMP[7:0]   | Output        | SDRAM Cont.                | SDRAM Array                | Byte Mask                                   |

| O_SRASN        | Output        | SDRAM Cont.                | SDRAM Array                | Row Address Select<br>(RAS) Command         |

| Signal Name       | Input/Output | Source      | Destination | Description                                   |

|-------------------|--------------|-------------|-------------|-----------------------------------------------|

| O_SWEN            | Output       | SDRAM Cont. | SDRAM Array | Write Enable                                  |

| QB_ADDRP[26:3]    | Input        | Quick Bus   | SDRAM Cont. | Address                                       |

| QB_BURSTREQP      | Input        | Quick Bus   | SDRAM Cont. | Four-Doubleword (Burst)<br>Request            |

| QB_BYTEP[7:0]     | Input        | Quick Bus   | SDRAM Cont. | Byte Enable                                   |

| QB_CMDIDP[3:0]    | Input        | Quick Bus   | SDRAM Cont. | Command ID                                    |

| QB_WRDATAP[63:0]  | Input        | Quick Bus   | SDRAM Cont. | Write Data                                    |

| QB_RDACK_SDCP     | Input        | Quick Bus   | SDRAM Cont. | Read Data Acknowledge                         |

| QB_READP          | Input        | Quick Bus   | SDRAM Cont. | Read Request                                  |

| QB_SLSEL_SDC_DP   | Input        | Quick Bus   | SDRAM Cont. | Memory Access Request                         |

| QB_SLSEL_SDC_RP   | Input        | Quick Bus   | SDRAM Cont. | Register Access Request                       |

| QB_WRITEP         | Input        | Quick Bus   | SDRAM Cont. | Write Request                                 |

| RESETP            | Input        | _           | SDRAM Cont. | System Reset                                  |

| SCLKP             | Input        | Global      | SDRAM Cont. | System Clock                                  |

| SDC_D_CMDRDYP     | Output       | SDRAM Cont. | Quick Bus   | SDRAM Controller Data<br>Command Ready        |

| SDC_R_CMDRDYP     | Output       | SDRAM Cont. | Quick Bus   | SDRAM Controller<br>Register Command<br>Ready |

| SDC_RDDATAP[63:0] | Output       | SDRAM Cont. | Quick Bus   | Memory read data                              |

| SDC_RDLOCKP       | Output       | SDRAM Cont. | Quick Bus   | Read Return Lock                              |

| SDC_RDRDYP        | Output       | SDRAM Cont. | Quick Bus   | Register read ready                           |

| SDC_SDOEN         | Output       | SDRAM Cont. | SDRAM       | Data Out Enable                               |

Table 2.3

SDRAM Controller Alphabetical Signal List (Cont.)

# 2.7.1 Signal Descriptions

#### B\_SDOP[63:0] Memory Data In/Out

#### This 64-bit bus carries data between the SDRAM Controller and the SDRAM array. The bus operates as an input to the SDRAM Controller during read accesses, and as an output to the SDRAM array during writes. The SDC\_SDOEN signal controls the direction of this bus.

#### O\_SADDRP[13:0]

#### **Row/Column Address**

This 14-bit bus outputs the address for a given transaction. During a row address select (RAS) cycle, the SDRAM Controller drives row address information on this bus. During a column address select (CAS) cycle, this bus drives the column address. Refer to Section 2.6, "SDRAM Addressing," on page 2-6 for more information.

O\_SCASN Column Address Select (CAS) Command Output The SDRAM Controller asserts this signal when driving a column address to the SDRAM array. The controller also uses O\_SCASN, along with O\_SWEN and O\_SRASN, as a control signal for signaling commands such as mode register set, active, and precharge to SDRAM devices. Refer to Section 2.9, "SDRAM Commands," on page 2-16, for more information.

#### O\_SCSN Chip Select Output The SDRAM Controller asserts this signal to enable the SDRAM device.

#### O\_SDQMP[7:0]

#### Byte Enable

#### Output

This 8-bit bus operates as a byte mask for B\_SDOP[63:0] on write transactions. The following table shows the correspondence between the byte enable signals and the valid data bits.

| Byte Enable | Valid<br>Data Bits | Byte Enable | Valid<br>Data Bits |

|-------------|--------------------|-------------|--------------------|

| O_SDQMP[7]  | [63:56]            | O_SDQMP[3]  | [31:24]            |

| O_SDQMP[6]  | [55:48]            | O_SDQMP[2]  | [23:16]            |

| O_SDQMP[5]  | [47:40]            | O_SDQMP[1]  | [15:8]             |

| O_SDQMP[4]  | [39:32]            | O_SDQMP[0]  | [7:0]              |

#### Bidirectional

Output

2-12

O SRASN **Row Address Select (RAS) Command** Output The SDRAM Controller asserts this signal when driving a row address to the SDRAM array. The controller also uses O SRASN, along with O SWEN and O SCASN, as a control signal for signaling commands such as mode register set, active, and precharge to SDRAM devices. Refer to Section 2.9, "SDRAM Commands." on page 2-16, for more information.

#### O SWEN Write Enable

The SDRAM Controller uses this signal in two ways. The controller asserts this signal to indicate the current transaction is a write transaction. The controller also uses O SWEN, along with O SRASN and O SCASN, as a control signal for signaling commands such as mode register set, active, and precharge to SDRAM devices. Refer to Section 2.9, "SDRAM Commands," on page 2-16, for more information.

#### QB ADDRP[26:3]

#### Address

This 24-bit bus carries the read or write address from the Quick Bus to the SDRAM Controller. The SDRAM Controller, in turn, signals address information to the SDRAM device using the O SADDRP[13:0] signal. Refer to Section 2.6, "SDRAM Addressing," page 2-6, for more information.

The Quick Bus asserts this signal to indicate a burst

#### QB BURSTREQP

#### Burst Request

(four-doubleword) transaction.

#### QB BYTEP[7:0]

#### Byte EnableInput

The Quick Bus uses this 8-bit bus to indicate which bytes are valid on QB\_DATAP[63:0]. The SDRAM Controller passes this data to the SDRAM device using O SDQMP[7:0]. The following table shows the correspondence between the byte enable signals and the valid data bits.

#### Output

# Input

Input

| Byte Enable | Valid<br>Data Bits | Byte Enable | Valid<br>Data Bits |

|-------------|--------------------|-------------|--------------------|

| QB_BYTEP[7] | [63:56]            | QB_BYTEP[3] | [31:24]            |

| QB_BYTEP[6] | [55:48]            | QB_BYTEP[2] | [23:16]            |

| QB_BYTEP[5] | [47:40]            | QB_BYTEP[1] | [15:8]             |

| QB_BYTEP[4] | [39:32]            | QB_BYTEP[0] | [7:0]              |

#### QB\_CMDIDP[3:0]

#### Command ID

This 4-bit bus carries the command ID for each request from the Quick Bus. On read returns, the SDRAM Controller returns the command ID on the SDC\_RDMID\_RP[3:0] signal.

#### **QB\_DATAP[63:0]**

#### Write Data In

### This 64-bit bus contains write data from the Quick Bus.

#### QB\_RDACK\_SDCP

#### Read Data Acknowledge

#### Input The Quick Bus asserts this signal to acknowledge receiving input data from the SDRAM Controller.

#### **QB READP** Read Request

The Quick Bus asserts this signal to indicate a read request.

#### QB\_SLSEL\_SDC\_DP

### Memory Access Request

The Quick Bus asserts this signal to request a read or write transaction from the SDRAM Controller.

#### QB\_SLSEL\_SDC\_RP

#### **Register Access Request**

# Input

Input

Input

The Quick Bus asserts this signal to select an internal register in an SDRAM device for read or write access.

# **QB\_WRITEP** Write Request

#### The Quick Bus asserts this signal to indicate a write request to the SDRAM Controller.

#### RESETP System Reset Input Master system reset input. The SDRAM Controller is idle after reset.

# Input

Input

# Input

#### SCLKP System Clock

2-14

Master system clock input. All transactions occur on the rising edge of the clock.

#### SDC D CMDRDYP

#### SDRAM Controller Data Command Ready Output

The SDRAM Controller asserts this signal when capable of handling data requests. The SDRAM Controller deasserts command ready when the command buffer is full. Typically, command ready is asserted unless a burst request is pending.

#### SDC R CMDRDYP

#### SDRAM Controller Register Command Ready